You are here: start » na » reporting » wp_9_period_3

UniBoard achievements in Q4

With the EC funds distributed, work at UMAN finally got underway. A one-day meeting was organized in Manchester with the UORL group, to discuss the interface between beamformer/pulsar processing and the RFI mitigation parts of the processing chain. In spite of some slight setback, the layout of the board progressed well and is now 99% done. VHDL design and simulations continued at the other institutes, with a focus at JIVE and ASTRON on completing a suite of test firmware by the arrival of the first prototype board. Two digital engineers, funded by external projects, joined the correlator development at JIVE. Shanghai Observatory decided to join RadioNet FP7 in order to become partner in UniBoard; two engineers from ShAO are expected to pay an extended visit to Dwingeloo in Q2 of 2010. Finally, an internal JIVE/ASTRON UniBoard progress meeting was held in December 2009. All in all, the project remains on track, with some minor delays.

Documents:

- UniBoard digital receiver design (draft 2) Gianni Comoretto, et al., 08-10-2009

General activities in Q4:

- Face-to-face meeting UORL-UMAN, Manchester, 12-10-2009

- Internal JIVE/ASTRON progress meeting, Dwingeloo, 08-12-2009

- 2-weekly general telecons

Activities by institute in Q4:

ASTRON:

- 2-weekly internal technical meetings

- board layout ongoing (99% routed, cleaning and routing still to be done)

- with JIVE: firmware written to check pinning and power

- to improve the manufacturability and reduce cost adjustments of the board stackup were made. This has resulted in a time loss of about one month.

BORD:

- mathematical model of digital filter developed to determine filter prameters (weights, truncation)

- VHDL coding for polyphase filter and 16-point FFT (1st stage) has been validated and placed in UniBoard SVN repository.

- 65 nano technology T/H chips have been assembled on demonstration PCBs; first tests were successful

INAF

- completed design of the digital receiver filterbank

- started final VHDL coding for second stage digital filter

- review of complete design

- training in the use of SOPC tools

JIVE:

- with ASTRON: compiled a VHDL design to fill FPGA (all interfaces and DSP blocks) to check if power supplies are adequate

- with ASTRON: compiled and simulated VHDL designs to test first board: DDR3 interfaces, JTAG UART, 12C sensors

- detailed design for control interface included in the correlator design document

- control code for client side written

- visiting researcher Ying Xiang (from ShAO) joined the correlator development in October 2009

- senior digital engineer Ronald de Wild (ASTRON) has started working part-time for JIVE on correlator development in November 2009

KASI:

- work had not started in Q4

UMAN:

- identification of issues which will reflect on the development based on the hardware review

- knowledge exchange on the mathematical description of coherent dedispersion

- initial Matlab sketch of coherent dedispersion completed

UORL:

- real data sets obtained from Manchester, used for simulations

- definition of workplan with UMAN on pulsar machine implementation

Problems / Issues

- none

Issues - organisational, administrative or other problems foreseen

- none

Red flags - major problems

- none

Forward Look (Q5-Q6)

ASTRON:

- PCB layout finished and start of production of prototype (Q5)

- production of first board (beginning of Q6)

- 8-board production run (Q6)

BORD:

- definition of module at FFT output to adjust signal power to be transmitted to output FPGA

- linking various modules (filter statistics estimate module, etc) to the NIOS

- completion of T/H testing and continuation of fast ADC architecture design

INAF:

- completion of HDL coding of both FPGA cores

- integration of cores in common SOPC UniBoard structure

- study concerning quantization effects on the design to prepare VHDL coding (with BORD)

- definition of ADC interface (with BORD)

JIVE:

- board testing (with ASTRON)

- completion of FPGA designs to test 1 and 10 Gb and transceiver ports, control software interface, configuration memory

- VHDL description of correlation architecture

- main components of correlator design completed:

- packet receiver/sorter and delay module

- filter bank/FFT

- corner turning

- correlation engine and processed data output

- synchronization and control logic

- tests of correlator design

KASI:

- one KASI engineer will visit JIVE/ASTRON in Q5/Q6, to assist in hardware tests

UMAN:

- complete knowledge exchange and gathering for the coherent dedispersion description

- full implementation of Matlab models for coherent dedispersion

- test of Matlab models using existing data and comparison with current processing chains

- skeleton design for data routing and data paths

UORL:

- continuation of Matlab simulations on real data from Nancay telescope

- definition of RFI mitigation algorithms architecture (with UMAN), including Matlab model of this architecture

- test of gold model on synthetic and real data

- VHDL coding

Expected milestones/ deliverables

- hard and firmware design documents, month 11:

- hardware and digital receiver design documents were completed in months 9 and 10, correlator design document will be completed before the end of month 12, due to the late start of work at UMAN the pulsar binning machine design document will be delayed to the end of Q5.

- first generation board, month 17:

- currently first prototype board is expected in month 16

- Expenditures - equipment, material and services:

- The complete UniBoard hardware budget was spent in year 1 on 64 Altera FPGAs, various components and PCB manufacture.

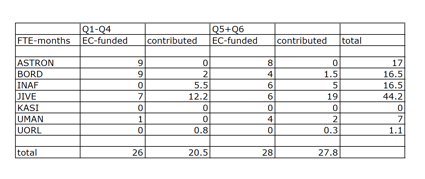

- Person month spent/to be spent until next EC Report

- Number of Persons working in JRA:

- currently 19